<This page is available in English>

QEMUモデリングサービス

弊社ではQEMUを用いた仮想ハードウェアモデルを短期間で構築するモデリングサービスを提供しています。QEMUはオープンソースのCPUエミュレータであり高速に動作し、ARMやRISC-Vといった様々なCPUに対応しています。ここでは弊社のQEMUモデリングサービスの特徴について説明します。

なお、QEMUに関する基本的な説明を以下の弊社の技術ブログで行っています。

割り込み出力に特化したモデル

仮想ハードウェアモデルの問題点

一般的に仮想ハードウェアモデルはSoC(System On a Chip)等の実機が完成する前に以下のような目的で使用されます。

- SoCの性能見積もり

- SoCを制御するためのソフトウェア(組み込みソフトウェア)の前倒し開発

また仮想ハードウェアモデルはARMやRISC-VなどのCPUやペリフェラル回路の動作をC/C++、SystemCと言った言語により記述するのが一般的です。

しかし仮想ハードウェアモデルには、モデル開発にコストと時間が思った以上にかかるといった問題があります。RTL設計など実際のハードウェア設計に比べると仮想ハードウェアモデルは短い期間で開発可能なのですが、やはりそれなりに工数はかかります。開発人数が少なすぎるとRTL設計よりも開発期間が長くなってしまうという本末転倒なことにもなりかねません。また、SystemCやQEMUといったフレームワークに関する知識も必要となりモデリングへの障壁が高くなっています。

割り込みに特化し、モデリング工数を大幅削減

弊社のQEMUモデリングサービスでの仮想ハードウェアモデルには大きな特徴があります。それはSoC内の周辺回路(ユーザ回路を含む各ペリフェラル回路)のモデルは割り込み出力に特化したものとなっている点です。

割り込み出力に特化したモデルとは例えば、

「周辺回路AにおいてレジスタBに対してCPUから書き込みがあれば3ms後に割り込みコントローラに対して割り込みを出力する」

といった具合です。例えば周辺回路が画像処理回路である場合、実際には実装される画像処理の詳細な動作などはモデリングしません。またSoCバスでのアービトレーションについてもモデリングはしません。

なお、割り込みを出力するための各種条件については必要に応じてモデリングします。

割り込み出力に特化したこのような単純なモデルであっても、SoC制御ソフト開発において割り込みハンドラの開発などでは有用であると弊社では考えています。

さらには周辺回路モデルから割り込み出力をランダムに生成することによりハードウェア故障を疑似的に発生させソフトウェアの振る舞いを確認する、といったことも可能となります。

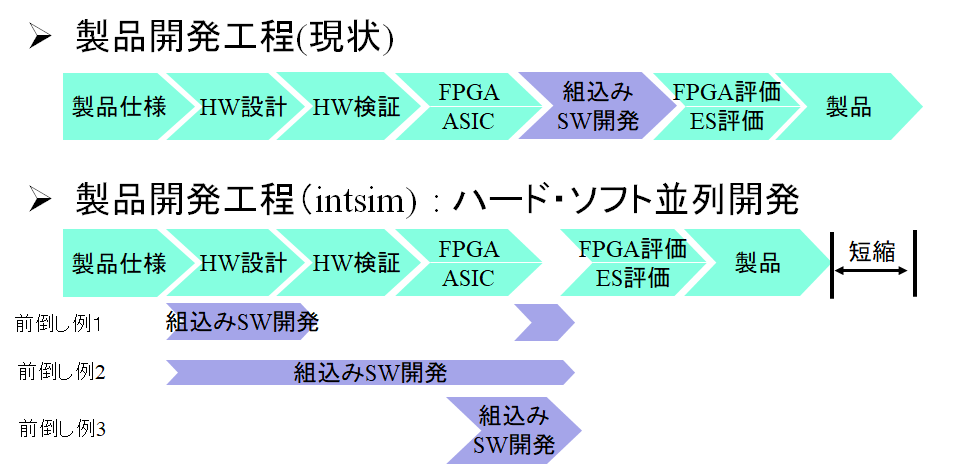

このように仮想ハードウェアモデルを割り込み出力に特化することにより下図に示すようなソフトウェアの大幅な前倒し開発が可能となります。

ソフトウェアの開発が大幅に前倒しできる理由は仮想ハードウェアモデル開発に必要な情報として各ペリフェラル(ユーザ回路含む)に対して以下があれば十分なためです。これらの情報はSoC開発においても比較的早い段階で用意できると考えられます。

- ペリフェラルのベースアドレス

- 周辺回路内の割り込み出力に関係するレジスタ情報(オフセットアドレス等)

- 割り込み発生時間(遅延)情報

また割り込み出力に特化しているためモデルが簡略化でき短期間でのモデル開発が可能となります。もちろん割り込み出力のみをモデリングしただけではソフトウェアとして確認できない事項はあるのですが、確認可能な事項も多数あると考えられます。

フレームワークとしてQEMUを利用

弊社の仮想ハードウェアモデルはフレームワークとしてQEMUを利用しています。QEMUはオープンソースのCPUエミュレータであり非常に高速に動作し、ARMやRISC-Vといった様々なCPUに対応しています。QEMUでは周辺回路(ペリフェラル)についてもモデリングが可能です。QEMUはQuick Emulatorの略で、読み方は、一般的には「キューエミュ」ですが「ケミュ」と呼ばれる場合もあります。QEMUはC言語で開発されている「ソフトウェア」であり、ペリフェラル回路モデルもC言語を使ってQEMUの作法に従い記述します。

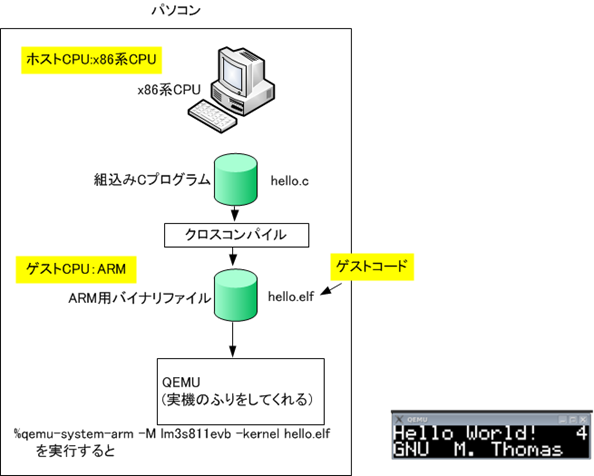

QEMUの利用イメージについて図 2を使って説明します。

図 2ではx86系のPC(パソコン)にてhello.cというCソースファイルを作成しています。Cソースファイル作成後、ARM用gccを使ってクロスコンパイルすることによりARM用バイナリ(実行ファイル:ELFファイル)を生成します。本来であればこのELFファイルを実機に送り込んで実機上で実行するのですが、今は実機が無いためELFをQEMUに渡して実行します。QEMU内部にてARM向けELFが実行されると、本来は実機上のディスプレイに「Hello World!」と表示されるべき文字列がPC内のウインドに表示されます(図 2の右下)。

図2ではQEMUを以下のように実行しています。

%qemu-system-arm -M lm3s811evb -kernel hello.elf

上記においてqemu-system-arm がQEMU本体であり、lm3s811evbが仮想ハードウェアのモデル名に相当します。弊社にてお客様向けに仮想ハードウェアをモデリングした場合は、このqemu-system-armという実行ファイルおよびCソースコードをご提供させて頂くことになります。qemu-system-armはスタティックリンクされたものであるためqemu-system-armだけあればお客様ではQEMU実行が可能となります。

今回はARMを例に説明していますが、弊社ではRISC-Vなど他のCPUにも対応可能です。

なお現時点(2024年11月)ではLinux版のQEMU 7.3.0に対応しています。Windows版QEMUには対応しておりません。

内製ユーティリティツールによりモデル開発を効率化

周辺回路のモデルを割り込み出力に特化するとは言え、QEMU用のCモデルを人手で作成するにはそれなりの知識と手間がかかります。このため弊社では内製のGUIユーティリティツール(intsim : Interrupt Simulator)を使用してQEMUモデリングの効率化を図っています。以降intsimについて紹介させて頂きます。

intsimの特徴

intsimの特徴は以下の通りです。

- QEMUモデリングのためのCコーディングは不要。各種情報を表形式にて入力するだけ

- QEMUモデルの生成からQEMUの実行までを自動化

- シミュレータの起動が容易

- ソースコードデバッガ(GUI)の起動が容易

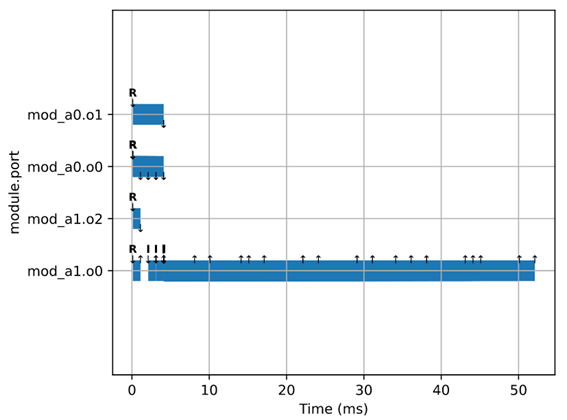

- 割り込み出力の様子をガントチャートにて表示

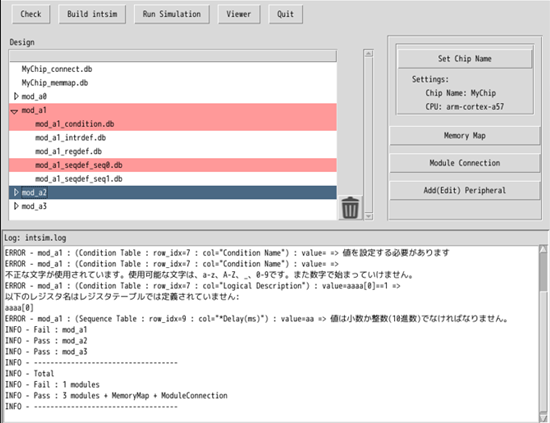

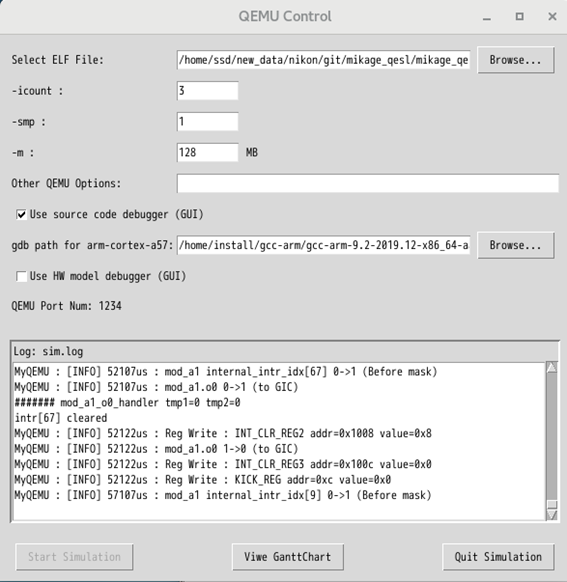

intsimのメイン画面は以下の通りです。

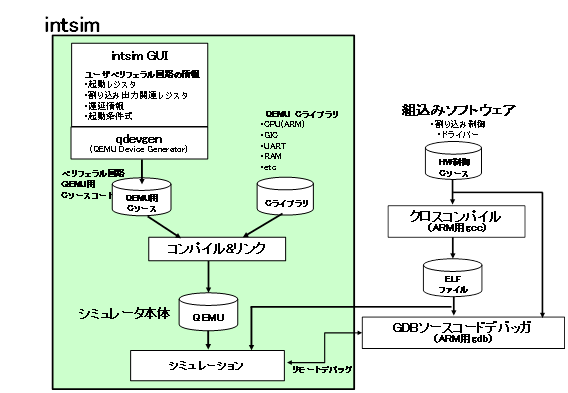

intsimの構成

以下にintsimの全体構成を示します。

上図に示すqdevgenも弊社にて開発したユーティリティツールです。

intsimによるモデリング例

intsimによるモデリングの流れは以下の通りです。

- 1.各周辺回路(ペリフェラル)における割り込み関連レジスタをGUIにて定義

- 2.各周辺回路(ペリフェラル)における割り込み出力をGUIにて定義

- 3.メモリマップ定義 : 各周辺回路(ペリフェラル)のベースアドレスをGUIにて定義

- 4.周辺回路(ペリフェラル)間の接続をGUIにて定義

- 5.シミュレーションをGUIから実行

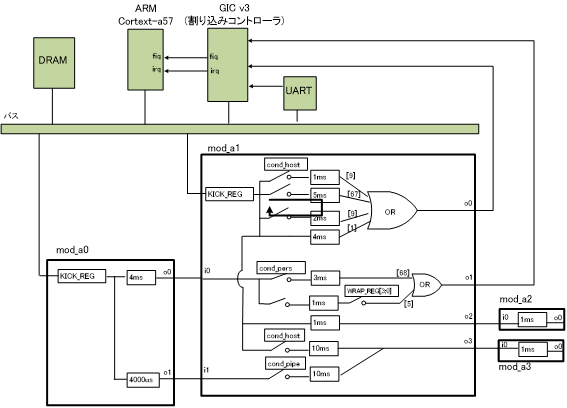

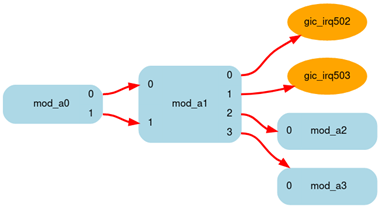

上記それぞれについてGUI設定画面の様子を簡単に紹介していきます。なお題材となるモデルを下図に示します。この図はintsimでのGUIとは関係なく、単に説明のために作成した図です。

弊社のQEMUモデルではペリフェラル間の接続もQEMUの割り込み機構を使って接続しています。例えば上図のペリフェラルmod_a0とmod_a1との接続がそうです。

なお、以降で示されるGUI設定画面と上図の内容は多少の差異がありますが、intsimの概要は理解して頂けると思います。

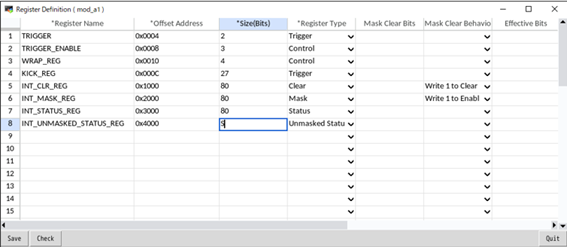

割り込み関連レジスタ定義

図 5中のmod_a1という周辺回路(ペリフェラル)に対するレジスタ情報の設定例を以下に示します。

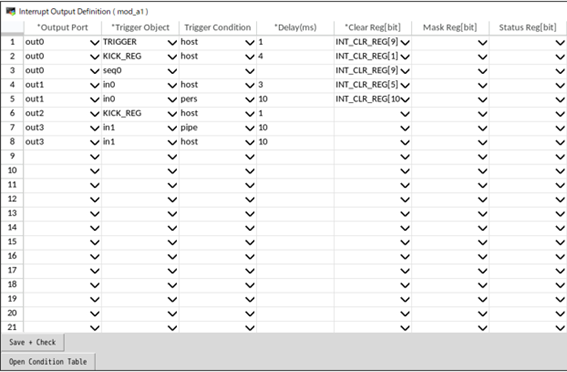

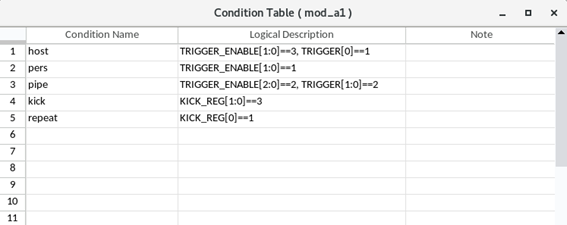

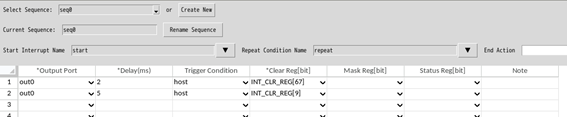

割り込み出力定義

図 5中のmod_a1という周辺回路(ペリフェラル)に対する割り込み出力定義の設定例を以下に示します。

上記表にはTrigger Conditionという列があり、たとえばhostという文字が入力されています。これはhostという条件が成立した場合に割り込みが出力されることを意味します。hostはユーザが定義した条件に対してユーザが付けた名前であり、条件定義テーブルにおいてその条件を定義します。条件定義テーブルを以下に示します。

上記条件定義テーブルでは、mod_a1内のレジスタTRIGGER_ENABLEのビット[1:0]の値が3でかつレジスタTRIGGERのビット[0]の値が1の場合に対してhostという条件名を付けています。条件はカンマで羅列し、モデルにおいては羅列した条件のANDが取られます。

割り込みシーケンスの定義

割り込み出力定義に対しては割り込みシーケンスの定義も可能となっています。割り込みシーケンスの例としては、

「割り込みAが発生した後、2ms後に割り込みBが発生し、割り込みBが発生した後5ms後に割り込みが発生し、その後割り込みBとCの発生を繰り返す」

と言ったものがあります。繰り返し条件や繰り返し終了後のレジスタ書き込み定義なども可能となっています。

図 5中のmod_a1に関する割り込みシーケンス定義の例を以下に示します。

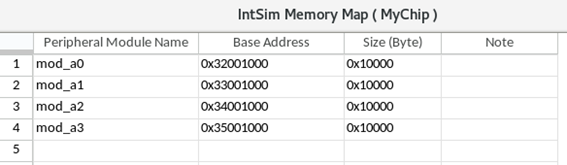

メモリマップ定義

以下にメモリマップ定義の設定例を示します。

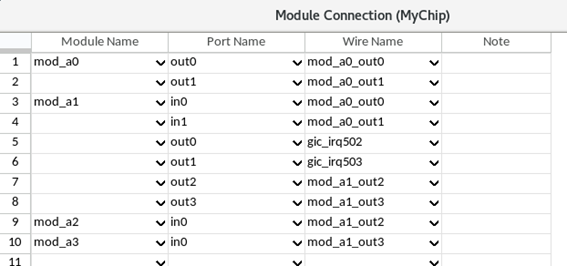

ペリフェラル間接続定義

以下にペリフェラル間接続定義の例を示します。

上記を入力した後、以下に示すブロック図を表示することも可能となっています。

シミュレーションの実行

ここまでGUIで入力すると以下のウインドにてELFファイルを指定してStart Simulationボンタンを

クリックしてQEMUを実行するだけです。UARTへ出力はログウインドに表示されます。

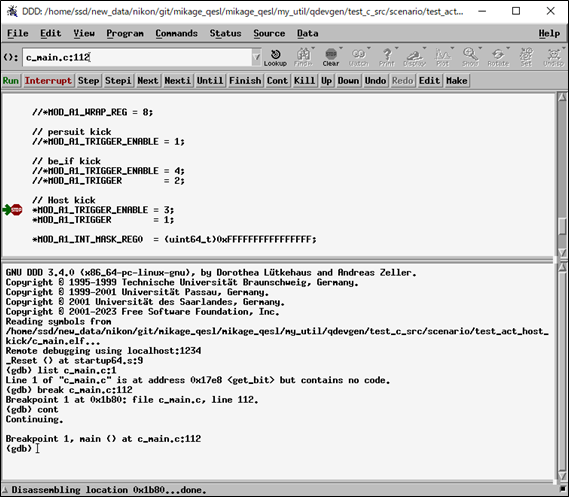

上記ウインド内の「Use source code debugger(GUI)」をオンにすると、以下のようにGUIソースコードデバッガとしてDDDを起動することも可能です。

またシミュレーション後は各割り込みの発生の様子を示すガントチャートを以下のように表示することも可能です。

まとめ

弊社のQEMUモデリングサービスでの割り込み出力に特化したモデル開発について紹介しました。周辺回路のモデルを割り込み出力に特化することにより短期間でモデルが開発でき、ソフトウェアとハードウェアの並行開発が可能となります。できるだけ早期に組み込みソフト開発を行いたいとお考えのお客様はぜひ弊社のQEMUモデリングサービスのご利用をご検討下さい。

問い合わせ先:qemu@profound-dt.co.jp